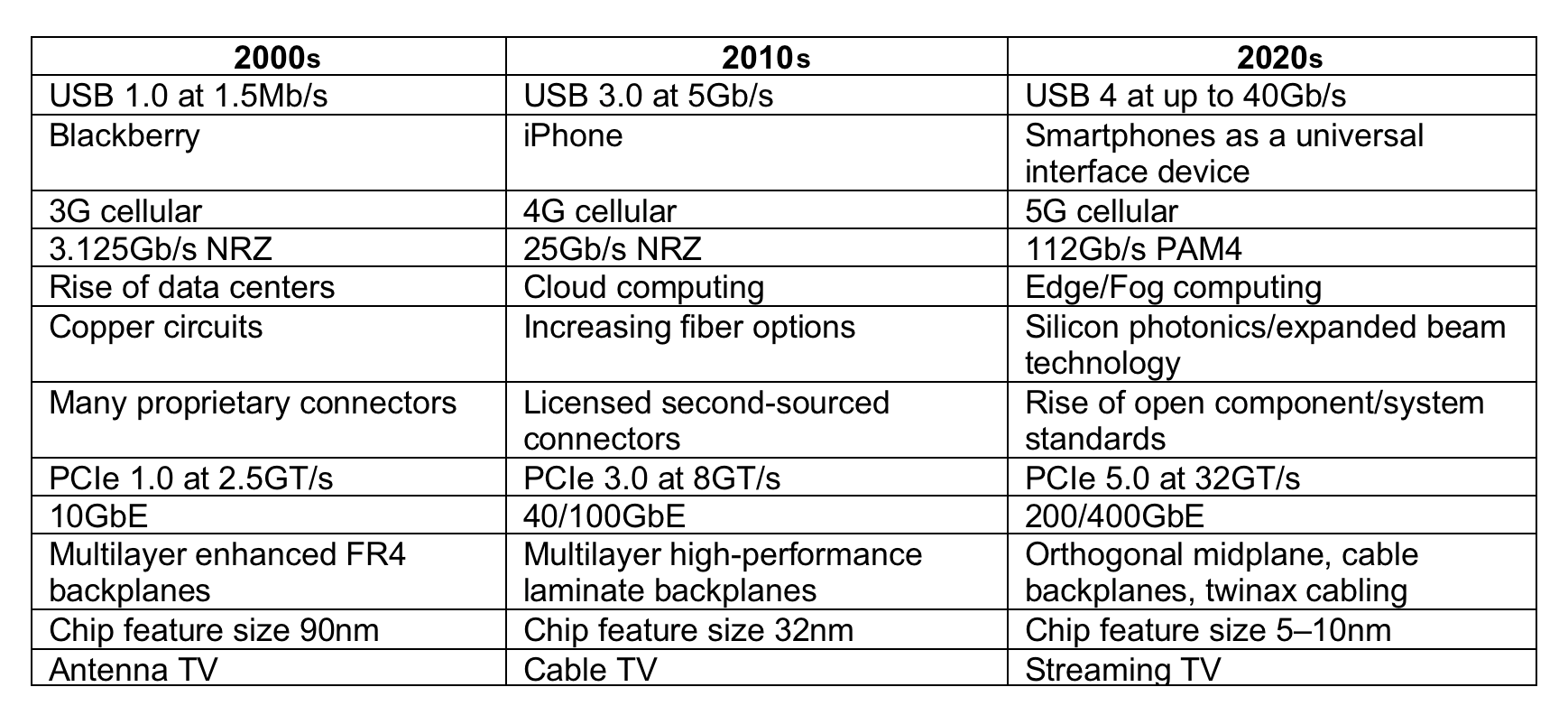

Top 12 Technology Trends: PCIe Specification Roadmap Evolves in Tandem With Increasing Bandwidths

A new generation of the PCIe specification is arriving this year, just in time to keep up with the growing demand for data fueled by 5G, cloud computing, AI, and other data-intensive connected technologies.

This seventh installment in the Technology Trends series by Bob Hult, a collection of articles that review leading technology trends that have had a significant impact on the electronic connector industry over the past 20 years, examines the evolution of the PCIe specification.

PCI Express, or PCIe, is an abbreviation for Peripheral Component Interconnect Express, a point-to-point, high-speed internal and external expansion bus protocol that has been a leading I/O communication specification since its introduction in 2003. The PCI Special Interest Group (PCI-SIG) created and maintains the PCIe specification with the help of its members, which includes more than 700 electronic component and equipment manufacturers.

In order to remain relevant in an environment of continuously increasing bandwidth demands, the PCI-SIG has driven the process of upgrading the PCIe specification in multiple iterations while maintaining full backward compatibility. A part of this process includes conducting compliance workshops to certify performance to this evolving standard.

The evolution of the PCIe specification has focused on the ability to support the enhanced requirements of Gigabit Ethernet.

The newest PCIe specification, PCIe 6.0, includes low-latency forward error correction (FEC) to improve bandwidth efficiency.

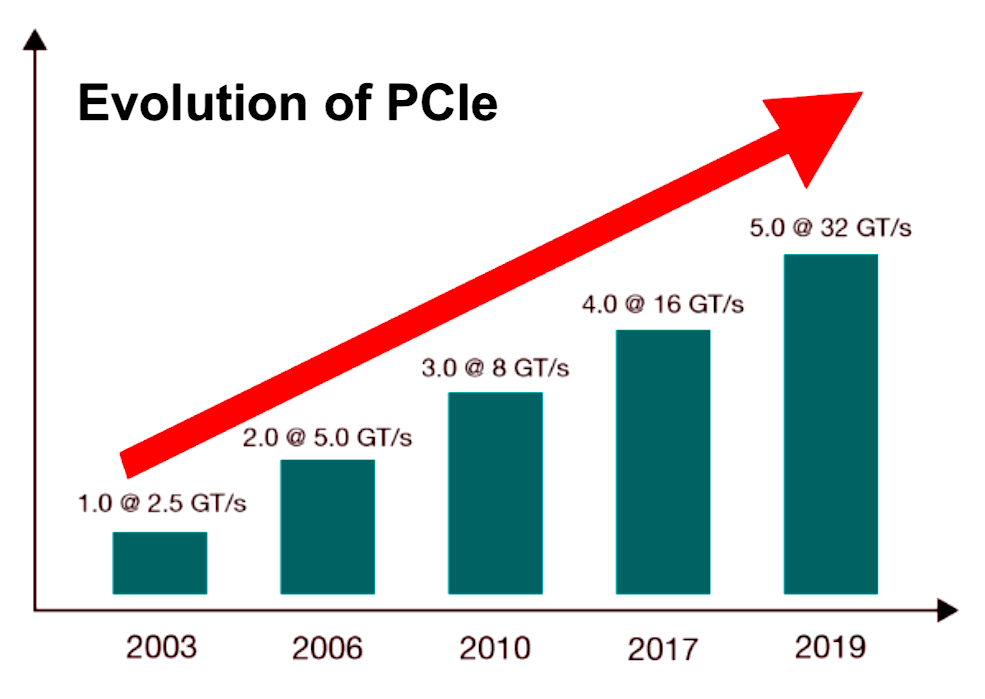

Due to the nature of its encoding scheme, PCIe expresses performance in terms of gigatransfers per second (GT/s) rather than the more common gigabits per second (Gb/s). Comparing data transfer rates between the two systems, a stated gigatransfer rate is somewhat higher than the calculated gigabit rate, reflecting overhead associated with the PCIe system.

In its original 2003 iteration, PCIe 1.0 enabled 2.5GT/s serial lanes. This generation of the standard was primarily focused on the personal computer industry.

The PCIe specification has evolved to accommodate higher bandwidths, with the current 5.0 iteration accommodating 32GT/s. That will double again when 6.0 is released later in 2021. (Image courtesy of Keysight Technologies)

PCIe 2.0 was introduced in 2006, doubled the speed to 5GT/s, and set the pace for the next several generations of expansion bus protocols.

In 2010, the PCIe 3.0 specification was released with a bit rate of 8GT/s per lane. A change in the encoding scheme significantly reduced overhead to the point of nearly doubling the data bandwidth of PCIe 2.0. This upgrade reflected demands driven by new applications in workstations and servers.

PCIe 4.0 required an unusually protracted seven years to develop and release. When it was finally introduced in 2017, it doubled performance to 16GT/s, with the ability to deliver 32Gb/s via the X16 configuration. Gen 4.0 also reduced power consumption. The first consumer products to implement PCIe 4.0 entered the market in early 2019.

Recognizing the need to respond more quickly to rapidly escalating demands of new data-intensive applications including servers, cloud computing, artificial intelligence, and 5G wireless, the PCIe Gen 5.0 specification was fast-tracked and released in May 2019, less than two years after the introduction of PCIe 4.0. Once again, the published maximum data rate of the prior generation was doubled to 32GT/s per lane with a total bandwidth of 128Gb/s. Signal integrity was also improved. The defined card-edge connector was optimized to support the higher bit rates while remaining backward compatible with prior iterations. The first silicon designed to support Gen 5 entered the market in mid-2019.

On June 18, 2019, PCI-SIG announced the development of PCIe 6.0, which will push data rates to 64GT/s per lane to deliver up to 256Gb/s in the X16 configuration. Gen 6.0 will be the first version of PCIe that will utilize PAM4 signaling and forward error correction. The connectors are expected to remain fully backward compatible with all prior versions of PCIe. The full PCIe 6.0 specification will be released in 2021.

A guiding principle of PCI-SIG has been maintaining backward compatibility of the defined card-edge connector. As bandwidth demands increased, the mechanical mating specification of the card electromechanical (CEM) PCB connector remained the same.

The standard connector prescribed in the PCIe specification is a low-cost, 1mm pitch, dual-row edge-card connector that has been modified with a special key to provide polarization and proper mating with the appropriate daughtercard. Connectors are available in vertical, right-angle, low-profile, and straddle-mount configurations, and support through-hole and wave solder termination to the PCB.

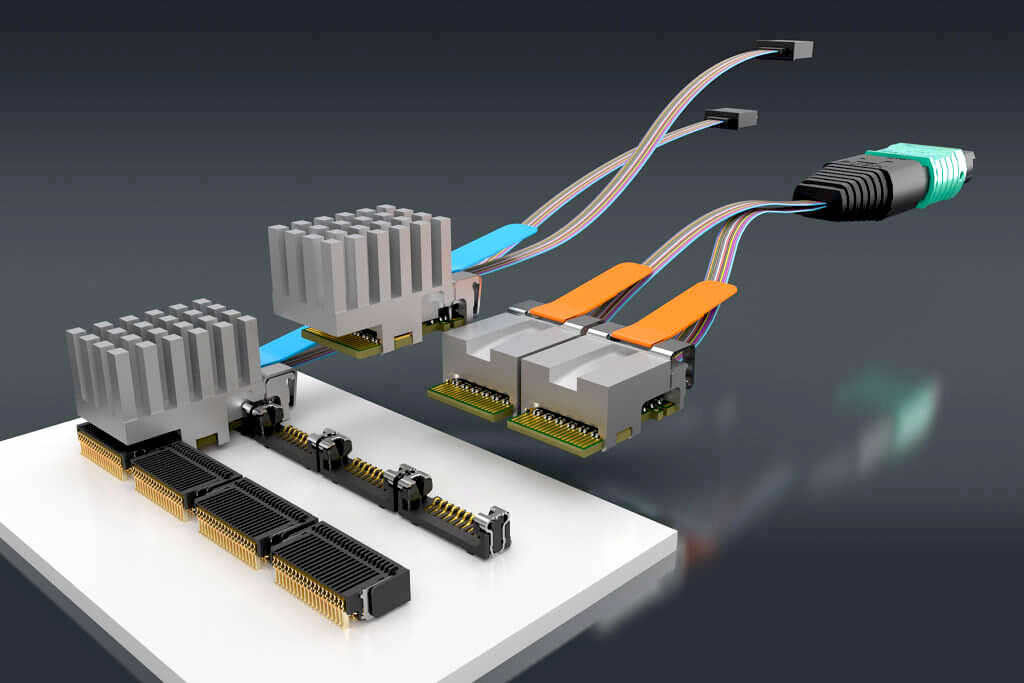

Samtec’s portfolio of high-speed board-to-board and backplane connectors includes several PCIe Gen 5 and Gen-5-compatible connectors.

PCIe motherboard connectors are available in four different sizes, consisting of 36, 64, 98, and 164 positions. Each offers corresponding lanes of bandwidth. Connectors are described as x1, x4, x8, and x16, based on the number of lanes of bandwidth they can support.

Typical applications include a mix of configurations to provide user flexibility.

The most recent generation, PCIe 5.0, upgrades the edge connector by adding a surface-mount version and a shorter mating wipe distance to minimize stubs. The mating PCB daughtercard was optimized with smaller gold fingers, improved vias and trace routings, and upgraded PCB laminate materials. The result has been improved channel performance.

PCIe can also be used in external cable applications. In 2007, PCI-SIG defined an external cable specification that allowed PCIe 1.0 and 2.0 to be implemented over copper cables.

The Molex iPass Connector System supports x4, x8, and x16 link widths. A D-subminiature connector is used for x1 applications. Internal and external I/O configurations are available.

In applications where exceptionally long channels are required, PCIe over optical fiber is the solution. Samtec offers a variety of PCIe-over-fiber technologies to address high-performance computing and data center applications with reach to 100 meters, including the new PCIe-Gen-4-Over-Fiber Adapter Card.

Samtec first highlighted its PCIe-over-fiber technology in a Samtec FireFly™ demonstration at OFC 2017.

The addition of an external cabling option opened the door to emerging applications in medical, instrumentation, external storage, video, and even military equipment.

The ongoing evolution of the PCIe specification is an excellent example of how legacy protocols can continue to thrive and support next-generation requirements.

Like this article? Check out the rest of Bob’s Technology Trends Series, I/O connectors, and Standards articles, our Datacom/Telecom Market Pages, and our 2020 and 2019 Article Archives.

- OFC 2026: High-Speed Networking in the AI Era - April 7, 2026

- DesignCon 2026 - March 17, 2026

- Breaking Through the AI Power Wall - January 20, 2026