What are PCIe Connectors?

Meet the Connector: PCIe Connectors

Peripheral Component Interconnect Express (PCle), also called PCI Express, is a high-performance and high-bandwidth serial communication I/O interconnect bus standard. Interconnects that meet the PCIe standard include mezzanine and board-to-board connectors, over-the-board solutions, high-speed edge card sockets that support 1, 4, 8, and 16 PCIe links, and PCIe optical cable assemblies.

PCIe connector on motherboard (image courtesy of Keysight Technologies)

PCIe is a layered protocol consisting of a transaction layer, a physical layer (subdivided into logical and electrical sublayers), and a data link layer (subdivided to include a media access control sublayer).

The PCIe link is built around dedicated unidirectional couples of serial (1-bit), point-to-point connections known as lanes. Every device connected to a motherboard with a PCIe link has its own point-to-point connection. (The earlier PCI connection was a bus-based system in which the devices competed for a bidirectional, 32-bit or 64-bit parallel bus.) PCIe significantly improves system throughput, scalability, and flexibility at lower cost than traditional bus-based interconnects.

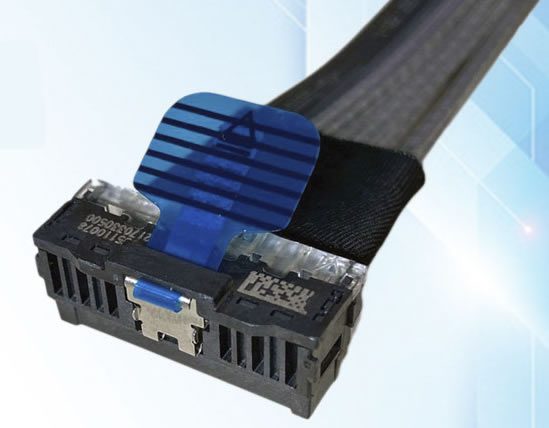

Amphenol Communication Solutions’ SAS/PCIe 5.0 (U.2 & U.3) connectors comes with 32 GT/s (PCIe lanes) and 24 Gb/s (SAS lanes) speeds to meet the demands of next-generation servers. The 68-position, SAS/PCIe receptacle and header enables implementation of high-speed Serial Attached SCSI (SAS) hard disk drive (HDD) interface as well as Peripheral Component Express (PCIe)-based devices. The molded guide post allows the device plug and receptacle to self-align during the mating process.

The first version of PCIe, 1.0a, was introduced in 2003 as a replacement for bus-based communication architectures such as PCI, PCI Extended (PCI-X), and Accelerated Graphics Port (AGP). It featured a per-lane data rate of 250 Mb/s and a transfer rate of 2.5 gigatransfers per second (GT/s). Each subsequent generation of PCIe has doubled the I/O bandwidth with new release every three years. The most recent iteration, the PCIe 6.0 specification, was released in January 2022.

Image 2 PCIe bandwidth growth across generations

Features of PCIe 6.0 include:

- 64 GT/s raw data rate and up to 256 GB/s via x16 configuration

- Pulse Amplitude Modulation with 4 levels (PAM4) signaling

- Lightweight Forward Error Correct (FEC) and Cyclic Redundancy Check (CRC) mitigate the bit error rate increase associated with PAM4 signaling

- Flit (flow control unit) based encoding supports PAM4 modulation and enables more than double the bandwidth gain

- Updated Packet layout used in Flit Mode to provide additional functionality and simplify processing

- Maintains backwards compatibility with all previous generations of PCIe technology

PCIe 7.0 specification is targeted for member release in 2025 and is anticipated to accommodate a 128 GT/s raw bit rate and up to 512 GB/s bi-directionally via x16 configuration.

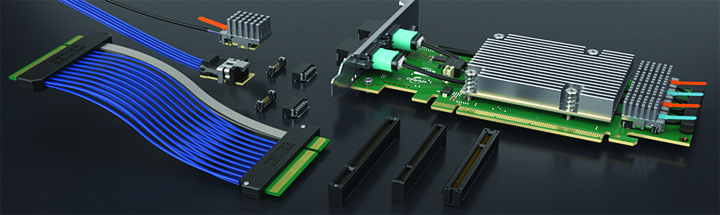

Molex’s NearStack PCIe Connector System and Cable Assemblies for next-gen servers were developed with the Open Compute Project. They use new direct-attached cable technology to improve signal integrity while lowering insertion loss and signal latency. Direct-to-contact twinax termination eliminates paddle cards within the cable assembly. Unlike competing cable jumpers, NearStack uses a fully automated wire termination process, which improves manufacturing efficiencies, repeatability, and signal integrity.

Design Notes

Standardization: PCl Express was initially proposed by Intel and further developed by the Peripheral Component Interconnect Special Interest Group (PCI-SIG), which continues to maintain and develop the standard.

Markets, Sectors, and Applications

Key markets include Automotive, Datacom/Telecom, Industrial, Military/Aerospace

Applications include artificial intelligence/machine learning, data center, high-performance computing, and IoT. PCIe is the common motherboard interface for PC graphics cards, hard disk drive host adapters, solid state drives, Wi-Fi, and Ethernet hardware connections.

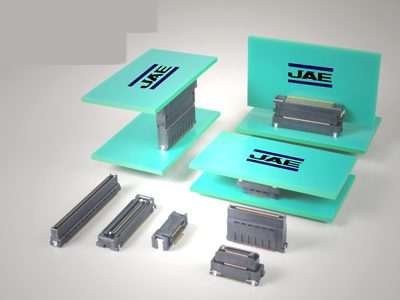

JAE’s AX01 Series floating board-to-board connectors support high-speed PCIe transmission.

Suppliers

Amphenol Communications Solutions, JAE, Molex, Samtec, TE Connectivity, ERNI Electronics, FCI/Amphenol, KYCON, KYOCERA AVX

Related products:

Subscribe to our weekly e-newsletters, follow us on LinkedIn, Twitter, and Facebook, and check out our eBook archives for more applicable, expert-informed connectivity content.

- Nurses Help Influence Interconnect Design - May 19, 2026

- What is SPE Cable? - May 12, 2026

- Automated Vehicle Manufacturing Accelerates with AI - May 5, 2026